Триггеры. Классы узлов

Триггер был создан до цифровой эры в виде реле для радиосхем. О его существовании рассказала статья в выпуске журнала The Radio Review от декабря 1919 года, а два десятилетия спустя триггер окажется в компьютере «Колосс», созданном в Англии для взлома немецких военных кодов, и в компьютере ENIAC в США.

Современные триггеры в неисчислимых количествах изготавливаются из транзисторов в интегральных схемах.

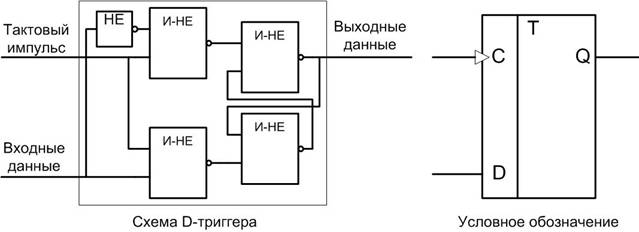

Одной из важнейших схем, применяемых в цифровой электронике, является триггер. Основное свойство триггера – способность запоминать и хранить логическое значение, что обусловлено наличием в схеме обратной связи. Если взять два инвертора и соединить, как показано на рисунке, получится простейший триггер.

При включении питания, на некоторых участках этой схемы установится состояние логического нуля, на других – логической единицы. Это состояние будет сохраняться до тех пор, пока питание не будет выключено. Неудобство этой схемы в том, что ее состояние непредсказуемо и неуправляемо. Однако если по аналогичному принципу построить более сложную схему с управляющими входами, ее можно будет использовать в качестве запоминающего элемента, способного хранить один бит информации.

В момент прихода тактового импульса такая схема запоминает состояние входа данных, и будет выдавать его на выход до прихода следующего тактового импульса. Эта схема имеет интересную особенность. Запоминание данных происходит не тогда, когда тактовый импульс имеет какое-то определенное логическое значение, а тогда, когда логическое значение тактового импульса переходит от логического нуля к логической единице. Принято говорить, что такой триггер синхронизируется по перепаду или фронту сигнала.

Существует много разновидностей триггеров, имеющих различные виды управления. По способу записи информации различают синхронные (тактируемые) триггеры, и асинхронные (нетактируемые) триггеры. В нетактируемых триггерах переход в новое состояние вызывается непосредственно изменением входных информационных сигналов. Например R-S триггеры, в которых имеются входы сброса и установки, и наличие логической единицы на одном из входов принудительно, независимо ни от чего переводит триггер в нужное состояние. В тактируемых триггерах имеется дополнительный вход управляющего сигнала и изменение состояния триггера происходит только при его наличии. Именно такой триггер мы только что и рассмотрели. По способу восприятия тактовых сигналов различают триггеры, управляемые фронтом, и триггеры, управляемые уровнем. Рассмотренная схема триггера представляет собой тактируемый триггер, управляемый фронтом.

Два класса узлов.

Хотя все узлы цифровой техники строятся из базового набора логических элементов, эти узлы можно разделить на два основных класса, имеющих фундаментальные отличия. Это узлы комбинационного типа, и узлы с памятью. Узлы с памятью иногда называют также схемами последовательностного типа. Принципиальные отличия состоят в следующем. Состояния выходов комбинационных схем зависит только от текущего состояния входов. Предыстория значения не имеет. В схемах с памятью, текущее состояние выходов зависит не только от текущего состояния входов, но и от состояния входов в предшествующие моменты времени. Простейшим примером схемы с памятью и является триггер.

Микросхемы интегральных триггеров.

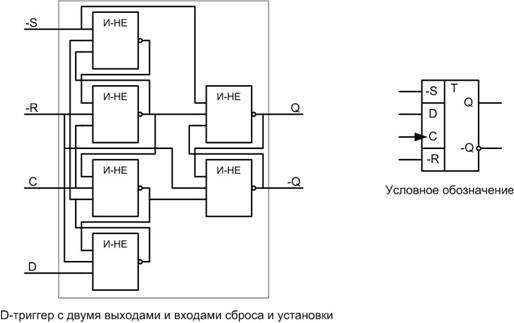

В одном корпусе таких микросхем обычно выполняют несколько специализированных триггеров и вспомогательных логических элементов управления их входами (схемы входной логики). В зависимости от структуры схемы входной логики получают триггеры с разными функциональными возможностями, подразделяемые на следующие типы: RS, RSC, Д Г, JK и др.

По способу управления триггеры подразделяют на асинхронные и синхронные (тактируемые). Переключение асинхронных триггеров происходит непосредственно с поступлением входного сигнала на их информационный вход. Синхронные триггеры имеют дополнительный тактовый вход С для подачи тактового импульса. Переключение триггера (или опрокидывание) происходит только при одновременном поступлении входного и тактового импульсов.

Существуют однотактные (Г) и двухтактные, или двухступенчатые (ГГ), триггеры. Однотактные триггеры переключаются по переднему фронту тактового импульса, а двухтактные — по его срезу. Триггеры имеют два выхода: прямой 0 и инверсный Г, соответствующий обратному значению 0 (если 0 = 1, то Р=0, и наоборот, если 0 = 0, то Р= 1). Считают, что триггер находится в единичном состоянии, когда 0= 1 и Г=0, а в нулевом состоянии, когда 0 = 0 и Р= 1.

Вход, по которому триггер устанавливается в единичное состояние, называют входом S(set), а в нулевое — входом R(reset). На двух входах ^-триггера возможны четыре комбинации сигналов. Если 5= 1, R=0, триггер переходит в единичное состояние (0=1, Р= 0), если же 5=0, R= 1 — в нулевое (0=0, Р- 1). При установке на входах логических нулей (5=0, Л = 0) триггер сохраняет предыдущее состояние. Такую комбинацию входных сигналов называют нейтральной, или запоминающей (памятью). Если на входы одновременно поступают единичные сигналы (5= 1, /? = 1), то на обоих выходах появляются логические нули ((?= О и Р=0), и триггер утрачивает свои свойства, поскольку после окончания импульсов под воздействием внутренних факторов он может равновероятно установиться как в единичное, так и нулевое состояние. Такая комбинация входных сигналов является запрещенной для RS- триггера.

/?5-триггер, построенный на логических элементах ИЛ И-НЕ и переключающийся единичными входными сигналами, называют триггером с прямыми входам (рис. 6.3). Приведенный триггер на логических элементах ИЛИ-HE является аналогом /^-триггера с прямыми входами на транзисторах (см. рис. 6.1), в котором ?/вх, является входом 5, a UBx2 — входом R. Очевидно, что ?/вых, соответствует инверсному выходу Р, а ?/вых2 — прямому выходу Q.

Если /^-триггер выполнен на логических элементах И-НЕ (рис. 6.4, а), то для того чтобы он вырабатывал те же выходные сигналы, что и триггер с прямыми входами, необходимо подавать на его входы инверсные сигналы. Поэтому он называется RS-триггером с инверсными входами и в его условном обозначении (рис. 6.4, в) на входах интегральной схемы показаны знаки инверсии (кружочки).

Триггер работает следующим образом (рис. 6.4, б). Если 5=0, R= 1, триггер переходит в единичное состояние (Q= 1, Р= 0). Если 5= 1, R = 0, триггер переходит в нулевое состояние (Q= 0, Р- 1). Если же 5 = 1, R = 1, триггер сохраняет предшествующее состояние (состояние запоминания). При установке на входах логических нулей (5=0, R- 0) на выходе /?5-триггера с инверсными входами возникает неопределенность. Для устранения этого недостатка созданы другие типы триггеров. Кроме того, существуют специальные синхронные триггеры, которые переключаются только при наличии синхронизирующего импульса.

Рис. 6.3. Асинхронный /?5-триггср на логических элементах ИЛИ-НЕ: а — структурная схема; б — временные диаграммы; в — условное обозначение

Рис. 6.4. Асинхронный /^-триггер с инверсными входами на логических

элементах И-НЕ:

а — структурная схема; б — временные диаграммы; в — условное обозначение